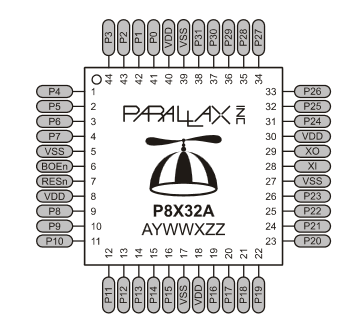

Parallax Propeller is multi-core microcontroller development platform. The Parallax P8X32A Propeller chip, introduced in 2006, is a multi-core architecture parallel microcontroller with eight 32-bit RISC CPU cores. It can be programmed for example with Propeller Assembly language, Spin interpreter and C programming languages.

Interesting news on this platform is that Parallax Propeller 1 Goes Open Source. On August 6, 2014, Parallax Inc. released the Propeller P8X32A Verilog and top-level HDL files under the GNU General Public License 3.0. I think it is a trust and an ecosystem thing: while is has a loyal following with hobbyists, it really hasn’t ever hit the big time. Propeller isn’t like traditional microcontroller, so it is a bit of a business risk to have vendor lock-in. Now you now no longer have to worry about second sourcing this part even if it went EOL.

If you are open hardware experimenter, you can now build a device that is open hardware, open code all the way down to the CPU level! Either use a product CPU, and have access to it’s source code to understand what and how it does things, or load that CPU onto a suitable FPGA and modify it or combine it with your design. By releasing the chip design, they would encourage people to try it out (as it is sold no or in a FPGA). Maybe this is way to try to survive on the market that is being taken over by different variations of ARM.