Nowadays you can find many low-cost microcontroller devboards (starting from just few dollars/euros). More recently, we’ve seen ARM Cortex kits for $10-$50, the flowering of the whole Arduino ecosystem, and of course, the Raspberry Pi. It’s microcontroller heaven with very many dev boards available. You you want more performance, there is a wide selection of Linux friendly single board computers in around $35 to $200 range.

What do you want to try next after microcontroller dev boards? Maybe FPGA. A field-programmable gate array (FPGA) is an integrated circuit designed to be configured by a customer or a designer after manufacturing. FPGAs contain programmable logic components called “logic blocks”, and a hierarchy of reconfigurable interconnects that allow the blocks to be “wired together” – somewhat like many (changeable) logic gates that can be inter-wired in (many) different configurations. Logic blocks can be configured to perform complex combinational functions, or merely simple logic gates like AND and XOR.

Those of us wanting a cheap “in” to the FPGA world have been less lucky than developers looking for microcontroller dev boards. FPGA boards under $100: Introduction article is indicting that the times, they are a changin’. Many FPGA devkits, from both chipmakers and third parties, have broken – or downright shattered – the $100 barrier, opening the door to low-cost FPGA prototyping, education, hobby projects, and so on. FPGA boards under $100: Introduction article offers a good overview of what is available.

Here are some interesting additions to the listed boards:

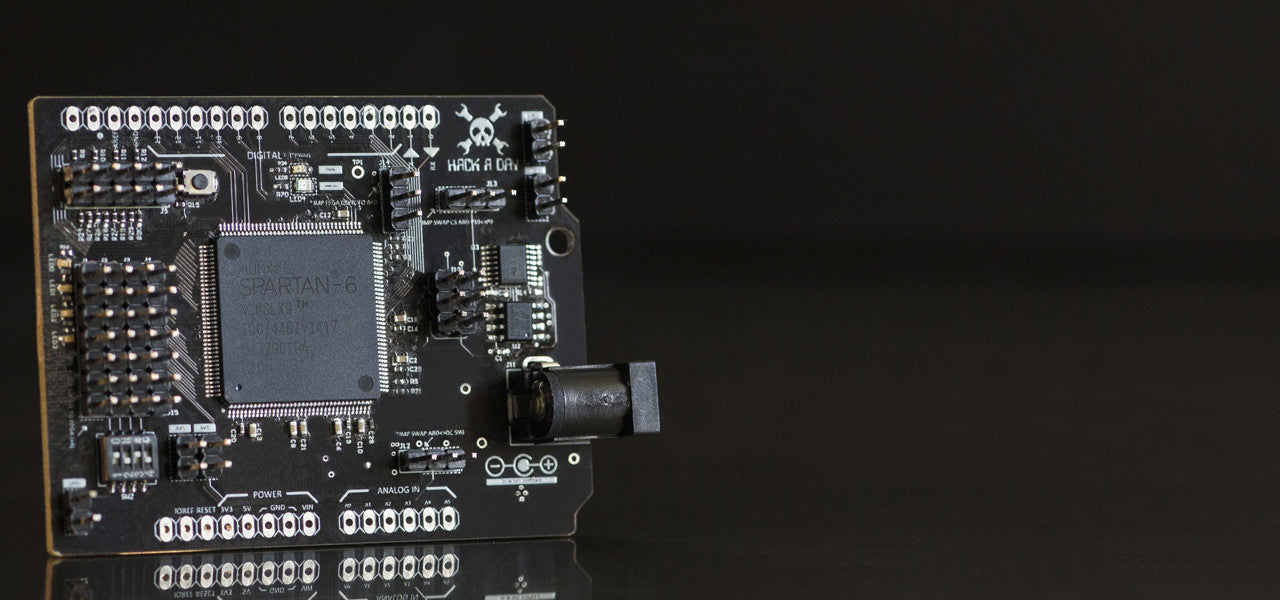

Hacklet 28 – Programmable Logic Hacks posting tells about Arduino-Compatible FPGA Shield. The shield features a Xilinx Spartan 6 FPGA and is available in The Hackaday Store. It has the needed regulators and level shifters. The price is $69.97. Not sure where to start? Check out Spartan-6 FPGA Hello World! that uses Xilinx’s free tool chain to getting a “hello world” led blinker running!

Hacklet 28 – Programmable Logic Hacks posting also mentions Chameleon. Chameleon is an Arduino compatible FPGA board with a Xilinx Spartan 3A FPGA on-board. The Chameleon Arduino-compatible shield board was designed to support two general application areas: (1) soft-core processors, and (2) intelligent serial communications interface.

Cheap FPGA-based HDMI Experimenting Board project is designing a (relatively) cheap little board for experimenting with HDMI using a Spartan-6 FPGA.

432 Comments

Tomi Engdahl says:

The ButterStick Is a Powerful Platform for Prototyping with the Lattice Semiconductor ECP5

Greg Davill’s latest hand-assembled PCB, the ButterStick, makes my work look like I’m all butterfingers!

https://www.hackster.io/news/the-butterstick-is-a-powerful-platform-for-prototyping-with-the-lattice-semiconductor-ecp5-8b878feebf4d

Tomi Engdahl says:

Embedded Hardware Accelerator with Xilinx Vitis: Part 1: Concept of Platform

https://highlevel-synthesis.com/2019/11/10/xilinx-vitis-part-1-concept-of-platform/

Goal: FPGA-based accelerator design flow is at the stage that software engineers can benefit from without an in-depth knowledge of hardware details. This series of blogs explain different methodologies for implementing efficient hardware accelerators for a wide range of compute-intensive tasks, using the Xilinx Vitis IDE platform.

Tomi Engdahl says:

Fully-featured FPGA development boards for a few bucks? That’s a hard find to pass up!

Fancy a Bit of Full-On FPGA Fun? These Days, It’s Far Cheaper Than You Might Have Feared!

https://www.hackster.io/news/fancy-a-bit-of-full-on-fpga-fun-these-days-it-s-far-cheaper-than-you-might-have-feared-07ba94171535

Tomi Engdahl says:

https://spectrum.ieee.org/geek-life/hands-on/painless-fpga-programming

Tomi Engdahl says:

Fancy a Bit of Full-On FPGA Fun? These Days, It’s Far Cheaper Than You Might Have Feared!

Fully-featured FPGA development boards for a few bucks? That’s a hard find to pass up!

https://www.hackster.io/news/fancy-a-bit-of-full-on-fpga-fun-these-days-it-s-far-cheaper-than-you-might-have-feared-07ba94171535

Tomi Engdahl says:

https://www.facebook.com/414718878625776/posts/3405366732894294/

And we have liftoff! Greg Davill’s ButterStick is a credit card-sized, ECP5-based FPGA board that’s now live on GroupGets via Hackster Launch: http://bit.ly/34nF6Tp

Tomi Engdahl says:

https://www.tomshardware.com/news/qomu-crowdsupply-mcu-fpga-dev-kit-thumbnail

Tomi Engdahl says:

https://theamphour.com/525-open-fpga-toolchains-and-machine-learning-with-brian-faith-of-quicklogic/

Tomi Engdahl says:

QuickLogic’s Tiny Qomu FPGA and MCU Dev Board, Designed with Sean Cross, Hits Crowd Supply

Packing a microcontroller, FPGA, dedicated sensor drivers, four touchpads, and even an RGB LED, the Qomu is tiny yet powerful.

https://www.hackster.io/news/quicklogic-s-tiny-qomu-fpga-and-mcu-dev-board-designed-with-sean-cross-hits-crowd-supply-8e92b10d9def

Tomi Engdahl says:

Wi-Fi bitstream programming for FPGAs, for a few bucks is pretty darn impressive.

The ESP32 Is the Chip That Keeps on Giving, This Time as a Wi-Fi JTAG Programmer for the ECP5!

https://www.hackster.io/news/the-esp32-is-the-chip-that-keeps-on-giving-this-time-as-a-wi-fi-jtag-programmer-for-the-ecp5-1319c7570c01

Wi-Fi bitstream programming for FPGAs, for a few bucks is pretty darn impressive.

Tomi Engdahl says:

Security In FPGAs And SoCs

How to make it more difficult for cyber criminals.

https://semiengineering.com/security-in-fpgas-and-socs/

Chip security is becoming a bigger problem across different markets, with different emerging standards and more sophisticated attacks. Jason Moore, senior director of engineering at Xilinx, talks with Semiconductor Engineering about current and future threats and what can be done about them.

Tomi Engdahl says:

Free To Good Home: FPGA Supercharged Audio/Video Synthesizer

https://hackaday.com/2021/03/03/free-to-good-home-fpga-supercharged-audio-video-synthesizer/

Audio and video synthesizers have been around for decades, and are pretty much only limited by one’s willingness to spend money on them. That is, unless you can develop your own FPGA-supercharged synthesizer to really get a leg up on the consumer-grade components. Of course, as [Julian] found out in this four-year project, you tend to pay for it anyway in time spent working on your projects.

[Julian] has actually decided to stop working on the project and open-source it to anyone who wants to continue on.

https://github.com/julianfl0w/zynqPCB

Tomi Engdahl says:

https://www.eetimes.com/xilinx-opens-up-vitis-hls-tool-for-fpgas/

Tomi Engdahl says:

Xilinx Adds a Mini Edition to Their UltraScale+ Line

Xilinx announces new 70% smaller form factor versions of their entire UltraScale+ FPGA lineup.

https://www.hackster.io/news/xilinx-adds-a-mini-edition-to-their-ultrascale-line-53918ad8259c

Tomi Engdahl says:

https://hackaday.com/2021/04/15/programming-pals-in-2021/

Tomi Engdahl says:

https://etn.fi/index.php/13-news/12193-avoimen-koodin-fpga-kortti-kehittajille

Tomi Engdahl says:

Slice Your Next FPGA Design

https://hackaday.com/2021/06/28/slice-your-next-fpga-design/

A recent trend has been to convert high-level constructs into FPGA code like Verilog or VHDL. Slice goes the other way: it converts very hardware-specific concepts to Verilog and aims to be a more expressive and easier to use language.

https://github.com/sylefeb/Silice

Tomi Engdahl says:

https://www.hackster.io/news/lattice-semiconductor-launches-certuspro-nx-fpga-family-with-bold-bandwidth-reliability-claims-226c2855fd67

Tomi Engdahl says:

https://www.hackster.io/news/the-lab-kiwi-aims-to-simplify-fpga-programming-offers-a-quick-start-smart-project-generator-37e0732a252c

Tomi Engdahl says:

https://www.element14.com/community/docs/DOC-96695/l/the-summer-of-fpgas-agenda

Tomi Engdahl says:

https://www.facebook.com/156088694417458/posts/6652689534757309/?substory_index=0

Save your spot at the element14 Electronics Arduino workshop tomorrow, where our very own Dario Pennisi will tell you everything you need to know about FPGAs and the MKR VIDOR 4000. You might even win a free board!

https://www.element14.com/community/events/5800/l/arduino-workshop-freedom-of-fpga-with-mkr-vidor-4000-win-a-free-board

Tomi Engdahl says:

The ICEd ESPresso Is a Cool, Refreshing Approach to Working with Two of Our Favorite Chips!

https://www.hackster.io/news/the-iced-espresso-is-a-cool-refreshing-approach-to-working-with-two-of-our-favorite-chips-6ca50670b175

I’ve got an ICEd ESPresso here for… “Hackers?” Did any Hackers order an ICEd ESPresso?! With extra FPGA and Wi-Fi?

Tomi Engdahl says:

Open Source SoC: The NEORV32 Processor

The NEORV32 is an open source microcontroller-like system on a chip (SoC) written in platform-independent VHDL.

https://www.hackster.io/news/open-source-soc-the-neorv32-processor-061f5219c45a

Tomi Engdahl says:

Hey, MiSTer Emulator, Gimme Almost Any Classic Platform!

https://hackaday.com/2021/09/12/hey-mister-emulator-gimme-almost-any-classic-platform/

At its heart is a dev board containing an Intel Cyclone SoC/FPGA, to which a USB hub must be added, and then a memory upgrade to run all but the simplest of cores. Once the hardware has been taken care of it almost seems as though there are no classic platforms for which there isn’t a core, as a quick browse of the MiSTer forum attests. We are treated to seamless switching between SNES and NED platforms, and even switching different SID chip versions during a running Commodore 64 demo.

Tomi Engdahl says:

https://hackaday.com/2021/09/26/fpga-retrocomputer-return-to-moncky/

Tomi Engdahl says:

Nick Matthijssen’s Open Source FPGA Craft Puts a Minecraft Clone on Your Lattice iCE40 FPGA

Muon developer puts a fully-functional voxel game on the FPGA at the heart of the low-cost open-hardware iCEBreaker board.

https://www.hackster.io/news/nick-matthijssen-s-open-source-fpga-craft-puts-a-minecraft-clone-on-your-lattice-ice40-fpga-345a9d41865d

Tomi Engdahl says:

FPGA on a 40-pin package boosts performance on the C64 and Apple II.

65F02 Is a 100 MHz Drop-In Replacement for Vintage 8-Bit Computers

FPGA on a 40-pin package boosts performance on the C64 and Apple II.

https://www.hackster.io/news/65f02-is-a-100-mhz-drop-in-replacement-for-vintage-8-bit-computers-ef667b0ebed3

Microprocessors like the 8-bit 6502 from MOS Technologies were at their height of popularity during the 1980s and 1990s. A modern variant of the original design is still available today that runs up 14 MHz. However, Jürgen Müller’s latest project advances that number by an order of magnitude. The 65F02 is a 6502 pin and instruction compatible processor replacement that runs at 100 MHz!

65F02′s 40-pin DIP compatible PCB fits directly into a socket designed for a 40-pin IC. The top side has the Spartan-6 FPGA, Flash Memory, configuration switches, and an LED. The bottom side of the board contains decoupling capacitors, regulators, and logic level shifters.

The part number “65F02″ fits nicely into the 6502′s lineage. When MOS Technology first developed the 6502, it licensed the design to other chip manufacturers. Some of those had process variants. Later, the 65c02 emerged, which was a CMOS version. That particular style is still available today from Western Design Center (WDC), the last remnants of the original MOS company. That chip, however, “only” runs up to 14 MHz. Somewhat slow compared to today’s clock speeds, but blazing fast to the original 2 MHz limit.

Internally the 65F02 runs at 100 MHz. However, external bus access operates slower to accommodate system buses that are not ready for 40 years of computing advancements. In addition, 65F02 mirrors external video memory to internal fast RAM to make video operations faster.

Addressing RAM on older systems did present a challenge. The original 6502 had a 16-bit address bus, which means it could only access 64 kilobytes of memory space. As a result, most computers implemented bank switching to address more memory. However, each computer design took a different approach.

Müller made all of 65F02′s design files available. For the schematic and PCB, there are Eagle files. You need Xilinx WebISE 14.7 if you want to modify the FPGA code. And to program the FPGA, Müller used the same programming hardware used in the TinyFPGA project.

http://www.e-basteln.de/computing/65f02/65f02/

Tomi Engdahl says:

Vidbo: Graphical HDL Simulation Over Web Sockets

https://www.hackster.io/news/vidbo-graphical-hdl-simulation-over-web-sockets-3ec96d377715?c4525d4b0ad85bb7ed6e5f31fbe008ce

A neat open source project, Vidbo is a web server that facilitates graphical interface HDL simulations for FPGA development.

Most FPGA developers/engineers will agree that one of the headaches of designing is getting a good simulation set up to prove in the HDL design’s functionality. Pretty much all of the IDEs for the FPGA chips out there (Vivado, Libero, etc.) have built-in simulators, but they don’t always provide an intuitive view of what’s going on. Olof Kindgren saw this gap in the market and addressed it with his latest open source project, Vidbo.

Vidbo, short for virtual board, is a web server with a graphical interface with a protocol created to communicate with a simulated FPGA development board or chip via web sockets.

Vidbo is the marriage of two previous projects of virtual development boards for HDL design and Verilatio which was the first revision of the web socket communication protocol with the HDL simulator.

The example project in the main Vidbo repository simulates a Nexys A7 board from Digilent with Verilog and C++ that implements the backend functionality of each component and HTML/SVG that comprises the front end web browser GUI

https://github.com/olofk/vidbo

Tomi Engdahl says:

Oak Development Technologies’ IcyBlue Feather Is a Breadboard-Friendly FPGA Dev Board

Built around a Lattice Semi ICE5LP4K FPGA, this Feather-format development board aims to lower barriers to entry.

https://www.hackster.io/news/oak-development-technologies-icyblue-feather-is-a-breadboard-friendly-fpga-dev-board-f4e790468cb3

Tomi Engdahl says:

Priced under $25, or a hair under $30 with carrier board, the M.2 T-FPGA is a compact entry point for low-power FPGA experiments.

LILYGO’s T-FPGA Combines an Espressif ESP32-S3 with a Gowin GW1NSR FPGA on an M.2-Format Dev Board

Priced under $25, or a hair under $30 with carrier board, the M.2 T-FPGA is a compact entry point for low-power FPGA experiments.

https://www.hackster.io/news/lilygo-s-t-fpga-combines-an-espressif-esp32-s3-with-a-gowin-gw1nsr-fpga-on-an-m-2-format-dev-board-47fc1e5b1702

Tomi Engdahl says:

https://hackaday.com/2024/03/21/weird-things-to-do-with-fpgas/

There’s an old joke about how can you find the height of a building using a barometer. One of the punchlines is to drop the barometer from the roof and time how long it takes to hit the ground. We wonder if [Alexlao512] had that in mind when he wrote a post about unconventional uses of FPGAs. Granted, he isn’t dropping any of them off a roof, but still. The list takes advantage of things we usually try to avoid such as temperature variation, metastability, and the effects of propagation delays.

Unconventional uses of FPGAs

https://voltagedivide.com/2024/03/18/unconventional-uses-of-fpgas/

Tomi Engdahl says:

xn--nding-jua

/

UltranetReceiver

Public

A FPGA-based receiver for Behringers Ultranet (X32, P16-I, P16-M, etc.)

https://github.com/xn--nding-jua/UltranetReceiver